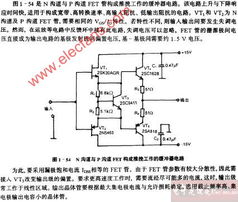

在数字和模拟电路中,推挽输出级因其高效率、低失真和强大的驱动能力而被广泛应用。其中,由互补的N沟道与P沟道场效应晶体管(FET)构成的CMOS推挽缓冲器电路,是实现这一功能的核心结构。下面将详细介绍其电路图构成与工作原理。

一、 基本电路结构

一个典型的N/P沟道FET推挽缓冲器(或称反相器、输出级)的简化电路图如下所示:

`

Vdd (电源正极)

|

|

+-+

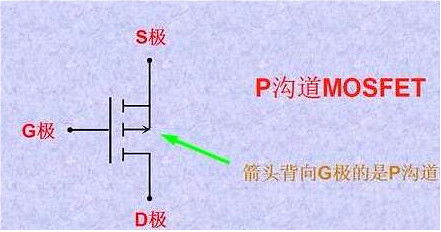

| | P沟道MOSFET (PMOS)

| | 源极(S)接Vdd

+-+

|

|---- 输出端 (Output)

|

+-+

| | N沟道MOSFET (NMOS)

| | 源极(S)接地(GND)

+-+

|

GND (电源负极/地)

(两管的栅极(G)连接在一起,作为输入端(Input);两管的漏极(D)连接在一起,作为输出端。)`

关键连接点:

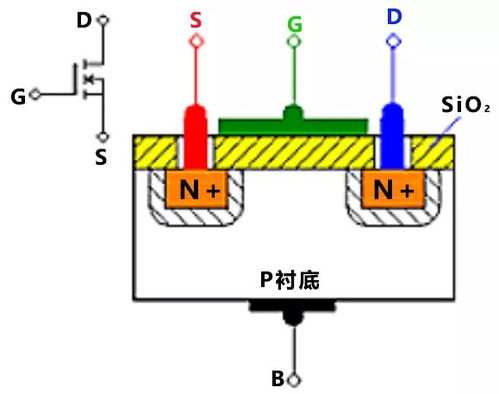

1. 输入端: PMOS和NMOS的栅极(G)相连,接收输入信号(Vin)。

2. 输出端: PMOS和NMOS的漏极(D)相连,提供输出信号(Vout)。

3. 电源连接: PMOS的源极(S)接正电源(Vdd);NMOS的源极(S)接负电源或地(GND)。

二、 工作原理(以数字逻辑为例)

该电路本质上是一个反相器,其工作状态由输入电压(Vin)决定。

- 当输入为高电平(Vin ≈ Vdd)时:

- PMOS: 栅源电压

Vgs ≈ Vdd - Vdd = 0V,小于其开启电压(Vthp,通常为负值),因此PMOS截止,相当于开关断开。

- NMOS: 栅源电压

Vgs ≈ Vdd - 0 = Vdd,大于其开启电压(Vthn),因此NMOS充分导通,相当于开关闭合。

- 输出结果: 输出端通过导通的NMOS强有力地拉低至地电平(GND),即输出低电平(Vout ≈ 0V)。此时从电源到地的静态电流通路被截止的PMOS阻断,功耗极低。

- 当输入为低电平(Vin ≈ 0V)时:

- PMOS:

Vgs ≈ 0 - Vdd = -Vdd,其绝对值远大于|Vthp|,因此PMOS充分导通。

- NMOS:

Vgs ≈ 0V,小于Vthn,因此NMOS截止。

- 输出结果: 输出端通过导通的PMOS强有力地拉高至电源电平(Vdd),即输出高电平(Vout ≈ Vdd)。同样,静态功耗近乎为零。

- 在输入电平切换过程中(过渡区):

- 会有一个短暂的时刻,输入电压处于PMOS和NMOS的阈值电压之间,导致两管同时微弱导通,形成一条从Vdd到GND的瞬时电流通路(称为“穿通电流”或“交越电流”)。这是动态功耗的主要来源之一。良好的设计会力求缩短这个过渡时间。

三、 作为缓冲器的特点与优势

当此电路用作输出缓冲器(Buffer)时,它并非总是以反相器形式出现(前端可加入反相级以实现同相缓冲),但其输出级具备以下核心优点:

- 高输入阻抗: FET栅极是绝缘的,输入端几乎不索取电流,对前级电路负载极轻。

- 低输出阻抗: 无论在输出高电平还是低电平时,都有一个晶体管处于深度导通状态(工作在可变电阻区),能够提供较大的拉电流(PMOS)或灌电流(NMOS),从而驱动重的容性负载(如长导线、其他MOS栅极)或阻性负载,并加快电压跳变沿。

- 轨到轨输出: 输出电压摆幅可以非常接近电源电压Vdd和GND,充分利用了电源电压,提高了噪声容限和动态范围。

- 静态功耗极低: 在稳定逻辑状态下,总有一个管子截止,静态电流几乎为零。这是CMOS技术的核心优势。

四、 应用场合

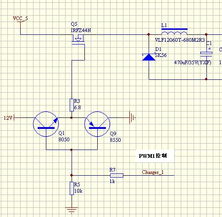

这种N/P沟道FET推挽结构是构成几乎所有现代数字集成电路(如微处理器、存储器)中逻辑门的基础。它也广泛应用于:

- 时钟驱动缓冲器

- 数据总线驱动器

- GPIO输出端口

- D类音频放大器的输出级

- 开关电源中的栅极驱动电路

###

由互补的N沟道和P沟道FET构成的推挽缓冲器电路,通过两管交替导通、截止的“推”与“拉”动作,实现了对输出节点的高效、强力驱动。其简洁的对称结构、近乎理想的静态特性以及优秀的动态性能,使之成为现代电子系统中不可或缺的基本电路单元。理解其工作原理是深入掌握数字电路与模拟输出级设计的关键一步。