在电子系统设计中,掉电(Power Loss或Power Down)是一种常见但危险的工况,可能导致系统状态丢失、数据损坏甚至硬件损坏。当使用N沟道和P沟道MOSFET作为电源开关或信号路径控制时,不恰当的掉电处理会引发系统出错。本文将探讨如何通过合理的电路设计和器件选型,有效防止掉电状况下系统因N/P沟道MOSFET引发的故障。

1. 理解掉电时的风险

掉电过程中,电源电压会从正常值逐渐下降至零。此时,MOSFET的栅极控制电压可能无法维持在有效电平,导致:

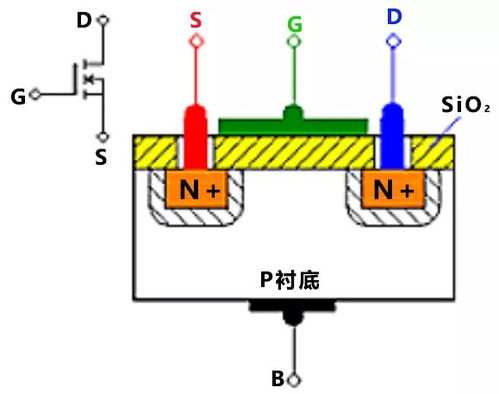

- N沟道MOSFET:通常用作低侧开关,栅极需要高于源极的电压才能导通。掉电时,若栅极电压先于电源电压下降,MOSFET可能意外关断,导致负载断电无序;若栅极电压因储能元件保持较高,可能意外导通,造成电流倒灌或短路。

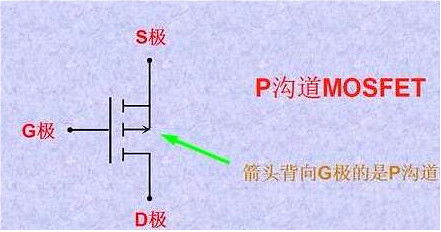

- P沟道MOSFET:通常用作高侧开关,栅极需要低于源极的电压才能导通。掉电时,源极电压下降可能快于栅极,导致MOSFET意外导通,形成反向电流路径,使系统各模块放电不均衡。

2. 关键设计原则

2.1 控制时序管理

确保MOSFET的开关状态在掉电时按预期变化:

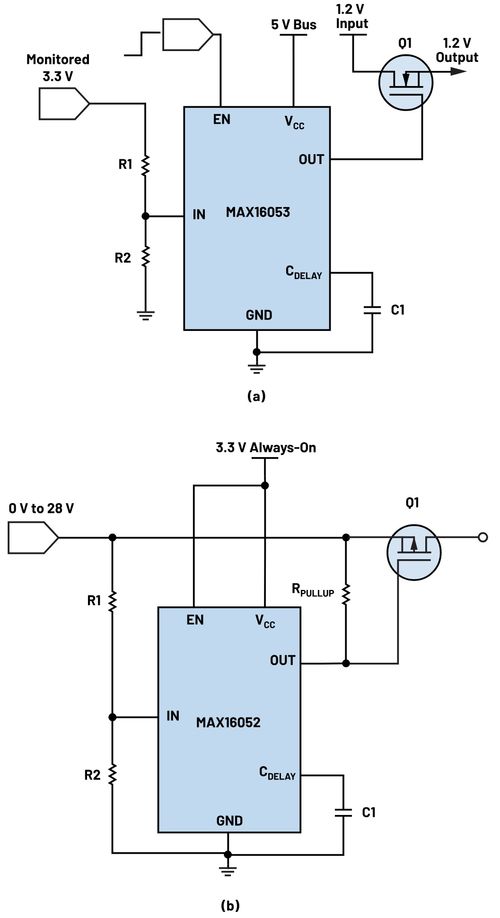

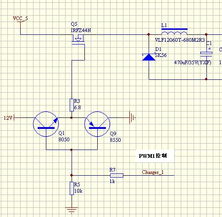

- 添加掉电检测电路:使用电压监控芯片(如TLV803)或RC电路检测电源电压,当电压低于阈值时,立即通过逻辑电路或MCU将MOSFET栅极置于安全状态(N沟道拉低、P沟道拉高)。

- 利用稳压二极管或专用栅极驱动芯片:在栅极串联稳压管(如BZX84系列),限制栅极电压范围,防止掉电时栅极电压浮动。对于高频开关,选用带欠压锁定(UVLO)功能的驱动芯片(如TC4420),在电压过低时强制输出高阻态。

2.2 防止反向电流

掉电时,负载侧电容可能通过MOSFET体二极管反向放电:

- 背对背MOSFET结构:对于双向电流控制,将两个同类型MOSFET串联(源极相连),使体二极管反向对接。掉电时,两个体二极管均不导通,可彻底阻断反向路径。此方法常用于电池保护电路。

- 串联肖特基二极管:在MOSFET的漏极或源极串联肖特基二极管(如BAT54),利用其低正向压降特性,优先于体二极管导通,防止反向电流。但会增加功耗和压降。

2.3 优化储能与放电路径

- 在栅极添加下拉/上拉电阻:N沟道MOSFET栅极接下拉电阻(10-100kΩ),确保掉电时栅极电压迅速归零;P沟道MOSFET栅极接上拉电阻至电源,确保掉电时栅极电压随电源下降,避免意外导通。

- 合理布局去耦电容:在电源入口处放置大容量电解电容(如100μF),延缓掉电速度,为系统提供关断时间;在MOSFET栅极并联小电容(1-10nF),减缓栅极电压变化,避免毛刺导通。

3. 针对应用的配置示例

3.1 电源开关电路(P沟道高侧开关)

Vin ──┬───源极(P-MOS)漏极─── Vout

│ 栅极

Cbulk │

│ Rpull-up (至Vin)

GND GND- 保护措施:

- 栅极上拉电阻Rpull-up(如100kΩ)确保掉电时栅极与Vin同步下降。

- 在Vin和Vout间并联肖特基二极管,防止Vout电容反向放电。

- 添加UVLO芯片控制栅极,检测到Vin低于阈值时强制拉高栅极。

3.2 负载开关电路(N沟道低侧开关)

Vcc ───负载───漏极(N-MOS)源极─── GND

栅极

│

Rpull-down (至GND)- 保护措施:

- 栅极下拉电阻Rpull-down(如10kΩ)确保掉电时快速关断。

- 在负载两端并联续流二极管,避免感性负载产生反向电压击穿MOSFET。

- 使用栅极驱动光耦或电平移位器,隔离控制信号与功率地。

4. 测试与验证

- 模拟掉电测试:使用可编程电源模拟电压斜坡下降(如从5V降至0V,斜率1V/ms),用示波器监测MOSFET栅极电压和负载电流,确保无异常导通或电压尖峰。

- 极端温度测试:在高温(+85°C)和低温(-40°C)下重复测试,验证器件参数漂移不影响保护功能。

- 长期可靠性测试:进行多次掉电循环(如1000次),检查MOSFET是否老化或损坏。

5. 选型建议

- 选择低Vgs(th)的MOSFET:降低对栅极电压的敏感度,但需权衡抗干扰能力。

- 优先选用逻辑电平MOSFET:在3.3V或5V系统中可直接驱动,避免额外电平转换电路引入故障点。

- 关注体二极管反向恢复时间:选择快恢复型MOSFET(如Infineon OptiMOS系列),减少反向电流持续时间。

###

防止掉电状况下系统出错,关键在于预测MOSFET在非理想工况下的行为,并通过冗余设计强制其进入安全状态。结合时序控制、反向电流阻断和储能管理,可大幅提升系统在掉电时的可靠性。实际设计中,应针对具体电源拓扑、负载特性和成本约束,灵活组合上述策略,并通过充分测试确保万无一失。