MOS管工作原理详解:N沟道与P沟道

1. 概述

MOS管(Metal-Oxide-Semiconductor Field-Effect Transistor,金属氧化物半导体场效应晶体管)是现代集成电路的核心元件,广泛应用于放大、开关及信号处理等电路中。它主要分为N沟道和P沟道两种类型,其工作原理基于电场对半导体导电沟道的控制。

2. 基本结构

无论是N沟道还是P沟道MOS管,其基本结构都包含以下部分:

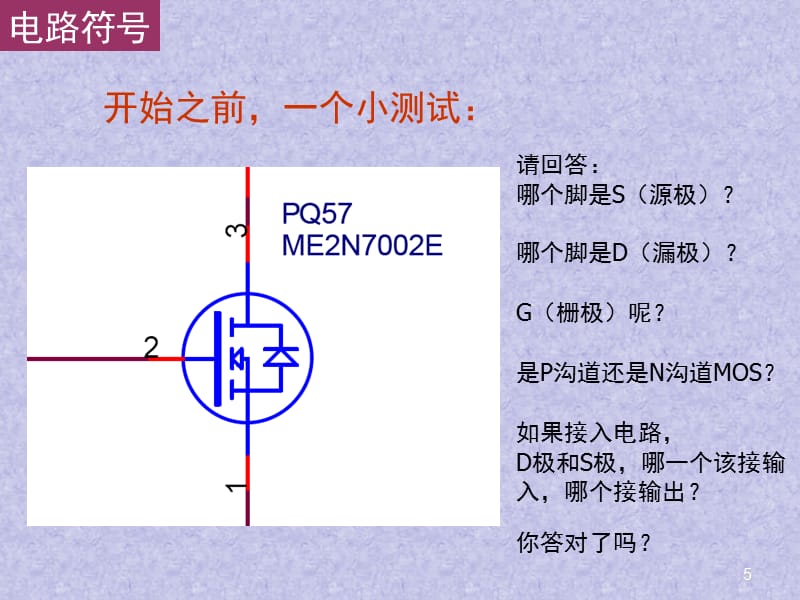

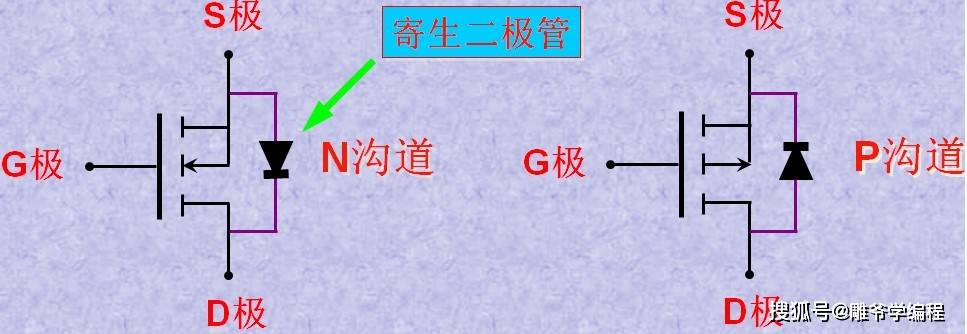

- 源极(Source,S):载流子流入的电极。

- 漏极(Drain,D):载流子流出的电极。

- 栅极(Gate,G):控制电极,通过施加电压来控制沟道的导通与关断。

- 衬底(Body/Bulk,B):通常与源极相连,以确定参考电位。

- 绝缘氧化层(SiO₂):位于栅极与半导体衬底之间,起绝缘作用。

2.1 N沟道MOS管(NMOS)

- 衬底为P型半导体(多数载流子为空穴)。

- 源区和漏区为N⁺型重掺杂区(多数载流子为电子)。

2.2 P沟道MOS管(PMOS)

- 衬底为N型半导体(多数载流子为电子)。

- 源区和漏区为P⁺型重掺杂区(多数载流子为空穴)。

3. 工作原理

3.1 N沟道MOS管工作原理

(1)增强型NMOS

- 截止状态:当栅源电压VGS = 0V或小于阈值电压VTH时,P型衬底中的多子(空穴)被吸引至衬底表面,形成耗尽层,源漏之间无导电沟道,电流I_DS ≈ 0。

- 形成反型层:当VGS > VTH时,栅极正电压吸引P型衬底中的少子(电子)至表面,排斥多子(空穴),从而在源漏之间形成一层以电子为多子的N型反型层,即N沟道。

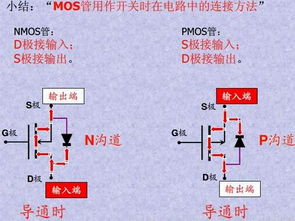

- 导通状态:沟道形成后,若在漏源之间施加电压VDS,电子将从源极经沟道流向漏极,形成漏极电流IDS。随着VGS增大,沟道变厚,导电能力增强,IDS增大。

(2)耗尽型NMOS

- 制造时已在栅极下方预置了N型沟道。

- 当V_GS = 0V时,沟道已存在,器件导通。

- 当V_GS施加负电压时,沟道电子被排斥,沟道变窄甚至消失,器件关断。

3.2 P沟道MOS管工作原理

(1)增强型PMOS

- 截止状态:当栅源电压VGS = 0V或高于阈值电压VTH(通常为负值)时,N型衬底表面无沟道形成,I_DS ≈ 0。

- 形成反型层:当VGS < VTH(施加负电压)时,栅极负电压吸引N型衬底中的少子(空穴)至表面,排斥多子(电子),形成以空穴为多子的P型反型层,即P沟道。

- 导通状态:沟道形成后,施加V_DS(通常为负压),空穴从源极经沟道流向漏极,形成电流。注意,PMOS中电流方向与电压方向通常与NMOS相反。

(2)耗尽型PMOS

- 预置P型沟道,V_GS=0时导通,施加正电压可耗尽沟道。

4. 特性曲线与关键参数

4.1 输出特性曲线(IDS - VDS)

- 可变电阻区:VDS较小,沟道完整,IDS随V_DS线性增加,类似可变电阻。

- 饱和区:VDS增大至VDS > VGS - VTH时,沟道在漏端夹断,IDS基本保持恒定,仅受VGS控制,用于放大。

- 击穿区:V_DS过大,发生雪崩击穿。

4.2 转移特性曲线(IDS - VGS)

- 反映栅压对漏电流的控制能力,定义了阈值电压V_TH。

4.3 关键参数

- 阈值电压V_TH:形成导电沟道所需的最小栅源电压。

- 跨导gm:反映栅压控制漏电流的能力,gm = ΔIDS / ΔVGS。

- 导通电阻R_ON:导通状态下源漏间的电阻。

- 极间电容:影响开关速度。

5. NMOS与PMOS对比

| 特性 | N沟道MOS管 (NMOS) | P沟道MOS管 (PMOS) |

| :--- | :--- | :--- |

| 衬底类型 | P型 | N型 |

| 多数载流子 | 电子 | 空穴 |

| 导通条件 | VGS > VTH (正电压) | VGS < VTH (负电压) |

| 电流方向 | 电子源→漏 (等效电流漏→源) | 空穴源→漏 (等效电流源→漏) |

| 载流子迁移率 | 高 (约是空穴的2-3倍) | 低 |

| 相同尺寸下性能 | 导通电阻小,速度快 | 导通电阻大,速度慢 |

| 常用领域 | 高速数字电路、存储器 | 常与NMOS组成互补结构(CMOS) |

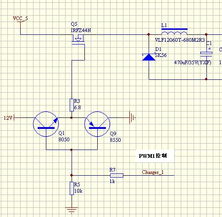

6. CMOS技术

将NMOS和PMOS组合使用,构成互补MOS(CMOS)电路。其主要优点是在静态时(非开关瞬间),总有一条支路截止,静态功耗极低,成为现代超大规模集成电路的主流技术。

7.

理解N沟道和P沟道MOS管的工作原理,关键在于掌握电场如何通过栅极电压控制半导体表面反型层(沟道)的形成与消失。NMOS依靠正栅压吸引电子形成N沟道,PMOS依靠负栅压吸引空穴形成P沟道。两者特性互补,共同构成了现代微电子技术的基石。在实际应用中,需根据电路需求(如速度、功耗、驱动能力)选择合适的类型或组合使用。